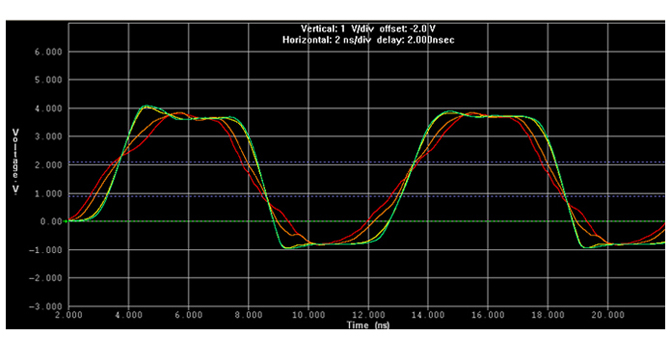

Learn when and how to apply signal integrity techniques to high-speed interfaces. This comprehensive course combines design techniques and methodology with relevant background concepts of high-speed bus and clock design, including transmission line termination, loading, and jitter. You will work with IBIS models and complete simulations. Other topics include managing PCB effects and on-chip termination. This course balances lecture modules with instructor demonstrations and practical hands-on labs.

Module 1: SI Basic terminology Introduction of Hyper lynx Basic of Simulation model (IBIS ) Layout translation method SI basic Data setup (Library, stack up, Pin Assignment, Power supply setup) Investigate stack-up strategies Pre and post Simulation method Line sim and Board sim simulation SI and Crosstalk issues Termination strategies Module 2: LineSim free-form schematic creation, editing stack-up, assignment of models and component values. Compare theoretical values with simulation results. Manual and automatic waveform measurements of overshoot, flight-time and crosstalk. Evaluating the effects of different impedance matching strategies, topologies, technologies, and stack-ups in LineSim Sweeping design parameters. Create and debug IBIS models. Perform Batch Mode Quick Analysis in BoardSim and review the report.

Copyright 2015 aura. All rights reserved.